Halbleiterspeicher für die Digitaltechnik

In jeder Datenverarbeitungsanlage gibt es Zentral- oder Arbeitsspeicher, wo Daten entweder fest eingespeichert sind oder je nach Bedarf eingelesen, zwischengespeichert, wieder ausgelesen, überschrieben oder gelöscht werden können. Eine einzelne Speicherzelle kann mit einem Bit die Information logisch 0 oder 1 speichern. Es lassen sich mehrere dieser Speicherzellen zusammenfassen,

die dann gemeinsam ein Datenwort zu einem Byte, das sind 8 bit speichern. Die Computertechnik arbeitet mit noch größeren Wortlängen, den ganzzahligen Vielfachen eines Bytes, zum Beispiel

16, 32 und 64 bit.

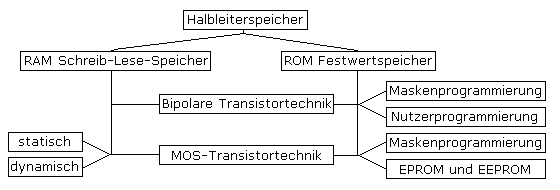

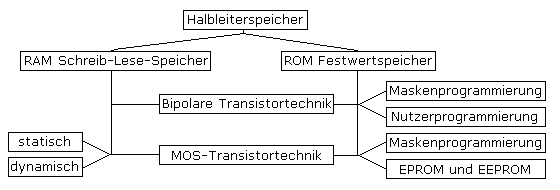

Das einzelne Speicherelement ist zumeist ein Halbleiterspeicher. Man unterscheidet zwischen Schreib-Lese-Speichern und Festwertspeichern. Beide Gruppen können in bipolarer oder MOS-Transistortechnik aufgebaut sein. Die Festwertspeicher sind entweder vom Hersteller maskenprogrammiert oder vom Nutzer selbst programmierbar. Einige lassen sich mehrfach löschen und neu programmieren.

Auf dieser Seite werden nach dem statischen RAM die folgenden Speicherbaugruppen in ihrer prinzipiellen Schaltung und Arbeitsweise beschrieben:

SRAM MOS–Technik, Dynamisches RAM, Maskenprogrammierte Festwertspeicher,

PROM Festwertspeicher, EPROM, EEPROM und MNOS / CT-Speicher.

Einheiten für Datenmengen

In der Informationstechnik, dem IT-Bereich, ist die kleinste Maßeinheit das Bit. Es ist ein zusammengesetztes Wort aus

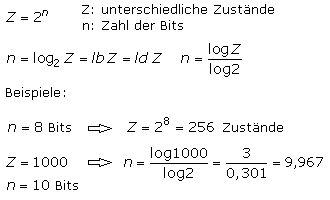

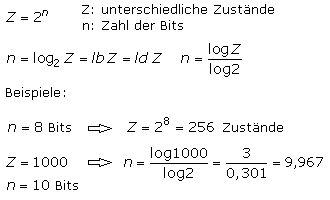

binary digit und im deutschen Sprachgebrauch mit Binärzahl übersetzt. Als Einheitenzeichen nach IEC als bit geschrieben. Nicht verwendet werden sollte das auch zu findende b für die Einheit. Ein Bit kann mit 0 oder 1, wahr oder falsch genau zwei unterschiedliche Zustandswerte Z darstellen. Mit zwei Bits können Z = 4 und mit 3 Bits Z = 8 verschiedene Zustände gekennzeichnet werden. Die maximale Zahl der unterschiedlichen Zustände Z errechnet sich mithilfe der Potenzreihe zur Basis 2 mit dem Exponenten n für die Zahl der Bits. Mit dem Logarithmus zur Basis 2, dem Zweier- oder binären Logarithmus kann die Zahl der notwendigen Bits ermittelt werden. Ist das Ergebnis eine Dezimalzahl, so muss es zur nächsten positiven Ganzzahl aufgerundet werden. Der Binärlogarithmus einer Zahl kann als ld(x) (Logarithmus dual) oder lb(x) (Logarithmus binär) geschrieben werden und mithilfe der im Beispiel gezeigten Methode mit dem dekadischen Logarithmus (log oder lg) der Taschenrechner umgerechnet werden.

Vier Bits als Gruppe zusammengefasst werden als Nibble oder Halbbyte bezeichnet. In der Speichertechnik wird derzeit das Byte als kleinste Einheit angesehen. Es umfasst 8 Bits zur Darstellung von maximal 256 unterschiedlichen Zuständen. Die Maßeinheit Byte ist mit dem Einheitenzeichen B zu kennzeichnen. Speicherkapazitäten werden meistens in Bytes und deren Vielfachen wie Kilobytes, Megabytes usw. angegeben. Für Übertragungsraten und Übertragungsgeschwindigkeiten erfolgen die Angaben in Bits, Kilobits, Megabits jeweils pro Zeiteinheit.

Große Mengen werden mit den Präfixen Kilo, Mega, Giga usw. versehen. Das genormte Internationale Einheitensystem passt mit den dezimalen Präfixen der

SI-Einheiten nicht zu großen binären IT-Datenmengen. Die direkte Verwendung ist zu vermeiden, sie führt zu fehlerhaften Ergebnissen und Verständnisproblemen. Die Tabelle zeigt nach dem IEC 60027-2 Vorschlag einen Auschnitt für das Binärsystem mit dem zusätzlichen Präfix bi und die an die

SI-Namensgebung angepassten Bezeichnungen und Symbole.

Im SI-Einheitensystem bilden die Präfixe ausgehend von kilo = 1000 eine Potenzreihe mit der Basis 1000. Im Binärsystem kommt der Wert 1024 dem nahe und wird als entsprechende Reihe mit kibi, mebi usw. bezeichnet. Je größer die Datenmenge ist, desto größer wird der Fehler, wenn zwischen binären und dezimalen Präfixen nicht genau unterschieden wird. Die folgende Tabelle zeigt für das Byte den zunehmenden Unterschied für dessen Vielfache in tausender Stufen. Das im Namenssymbol für Byte (8 bit) verwendete B ist keine SI-Einheit. Die Zahl der unterscheidbaren Zustände ist hier nicht angegeben und liegt wesentlich höher.

Statisches RAM

Zu den in Halbleitertechnologie aufgebauten random access memory RAM Arbeitsspeichern zählen alle Schreib-Lese-Speicher mit wahlfreiem (random) Zugriff. Die Speicherzellen sind in einer zweidimensionalen Matrix angeordnet. Mit ihrer eindeutigen Adresse, dem Kreuzungspunkt des Reihen- und Spaltenzählers sind sie gezielt ansprechbar. Der Speicherzustand jeder so ausgewählten Zelle kann beliebig oft gelesen oder verändert werden. Beim Lesen bleibt der Speicherinhalt erhalten. Ein Ausfall der Betriebsspannung löscht alle im RAM gespeicherten Informationen.

Die SRAM genannten statischen RAM-Elemente können in bipolarer TTL- und ECL-Technik sowie mit MOS-Feldeffekttransistoren hergestellt werden.

Bipolare Transistortechnik

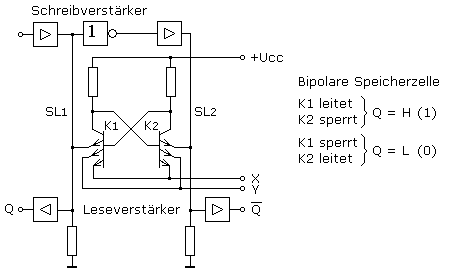

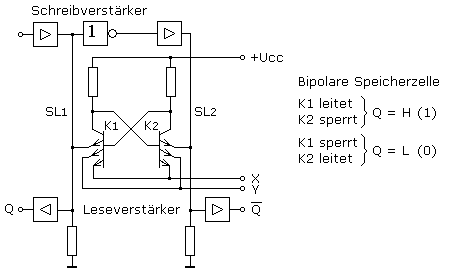

Das folgende Bild zeigt eine Prinzipschaltung in TTL-Technik für eine Flipflop Speicherzelle mit zwei Multiemittertransistoren. Die Speicherzelle hat die Koordinatenleitungen X und Y sowie mit SL1 und SL2 zwei Schreib-Lese-Leitungen. Mit leitendem Transistor K1 sperrt K2 und die Zelle speichert als Binärwert eine logische 1. Ist K1 gesperrt, dann leitet K2 und die Zelle speichert eine logische 0. Die Zelle ist nicht aktiviert, wenn mindestens eine oder beide Koordinatenleitungen mit 0 V an Masse liegen. Der Emitterstrom des leitenden Transistors fließt über diese Koordinatenleitungen nach Masse.

Aktivierung

Die Speicherzelle ist aktiviert, wenn bei der Betriebsspannung von +5 V an beiden Koordinatenleitungen mit +5 V High Pegel anliegt. Der Emitterstrom des leitenden Transistors kann nur noch über seine Schreib-Lese-Leitung fließen. Der entsprechende Leseverstärker wird mit einer positiven Eingangsspannung angesteuert.

Lesevorgang

In der Speicherzelle soll der Transistor K1 leitend sein und die Zelle den Binärwert 1 speichern. Nach der Aktivierung fließt der Emitterstrom durch die SL1-Leitung und der dort angeschlossene Leseverstärker zeigt mit High Pegel am Ausgang Q den Speicherzustand 1 der Zelle an. Der Transistor K2 ist in diesem Fall gesperrt und die SL2-Leitung stromlos. Der rechte Leseverstärker hat mit Low Pegel am Ausgang den Q-Nicht Zustand.

Bei einem in der Zelle gespeicherten Binärwert 0 ist der Transistor K1 gesperrt und K2 leitend. Nach der Aktivierung führt die SL2-Leitung Strom und die SL1-Leitung bleibt stromlos. Der Ausgang Q des linken Leseverstärkers zeigt mit Low Pegel den Speicherzustand 0 der Zelle. Der rechte Leseverstärker mit Q-Nicht hat High Pegel.

Der Leseprozess verändert den Speicherzustand nicht und kann beliebig oft wiederholt werden. Mit einer UND Verknüpfung des Q-Ausgangs und des invertierten Q-Nicht Ausgangs wird meistens die Sicherheit des Leseergebnisses optimiert. Mit Q = 1 ist das invertierte Q-Nicht = 1 und nur dann kann der Datenausgang High Pegel haben.

Schreibvorgang

Die Speicherzelle muss zuvor aktiviert werden. Die Leseverstärker werden während des Schreibvorgangs abgeschaltet. Mit High Pegel an der SL1-Leitung liegt gleichzeitig Low Pegel an der SL2-Leitung. Diese Kombination sperrt unabhängig von den bestehenden Verhältnissen den Transistor K1 und schaltet K2 in den Leitzustand. Damit wird in die Speicherzelle der Binärwert 0 geschrieben.

Wird von diesem Speicherzustand ausgehend der Binärwert in 1 geändert, dann muss bei aktivierter Zelle die SL1-Leitung Low Pegel und die SL2-Leitung High Pegel erhalten. Alle Basis-Emitterspannungen sperren mit 0 V den Transistor K2. Seine Kollektorspannung erreicht Betriebsspannung und steuert die Basis des Transistors K1 an, dessen Emitterspannung bei Low Pegel 0 V hat. K1 wird leitend und hält mit seiner nunmehr niedrigen Kollektorspannung von 0,3 V den Transistor K2 selbst gesperrt. Der Speicherzustand bleibt nach dem Schreibvorgang auch ohne Aktivierung erhalten.

△

MOS-Technik

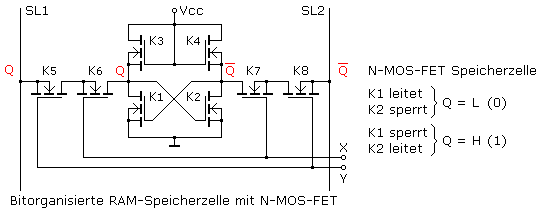

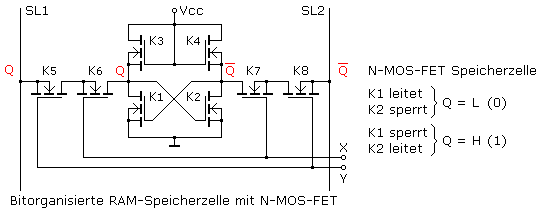

SRAM Arbeitsspeicher in TTL-Technik haben kurze Schaltzeiten und einen hohen Leistungsbedarf, da immer einer der Transistoren Emitterstrom leitet. Werden die Speicher mit MOS-Transistoren aufgebaut, erreicht man eine höhere Integrations- und somit Speicherdichte. Der Leistungsbedarf ist viel geringer aber die Schaltzeiten werden länger. Meistens werden die Speicherzellen mit selbstsperrendem

n-Kanal MOS-FET hergestellt. Das folgende Bild zeigt für ein Bit organisiertes statisches RAM die Prinzipschaltung einer Speicherzelle ohne Schreib- und Leseverstärker.

Die Transistoren K1 und K2 bilden mit den Arbeitswiderständen K3 und K4 das Flipflop. Die Zelle speichert den Binärwert 0, wenn K1 leitet und K2 gesperrt ist. Leitet der Transistor K1, dann ist seine Drainspannung nahezu 0 V und hält den Transistor K2 mit der Gate-Source-Spannung von 0 V gesperrt. Die Drainspannung K2 nimmt den Wert der Betriebsspannung an, wodurch K1 mit einer positiven Gate-Source-Spannung leitend gehalten wird.

Leseprozess

Liegt an beiden Adressleitungen X und Y eine ausreichend positive Spannung, dann werden mit den positiven Gate-Source-Spannungen die Transistoren K5 bis K8 leitend. An den Schreib-Lese-Leitungen SL1 und SL2 liegen die Drainspannungen des Flipflops. War K1 leitend, dann hat der Ausgang Q Low Pegel und Q-Nicht High Pegel.

Schreibprozess

Die Zelle wird mit High Pegel an beiden Adressleitungen aktiviert. Soll das Flipflop den Binärwert 0 speichern, dann muss der Schreibprozess den Transistor K1 leitend steuern. Mit einem High Pegel an der SL2-Leitung erhält der Flipflop-Ausgang Q-Nicht ebenfalls High Pegel. Das positive Drainpotenzial von K2 steuert K1 mit positiver Gate-Source-Spannung leitend. Der Q-Ausgang des Flipflops hat Low Pegel und hält auch nach dem Schreibvorgang und Deaktivieren der Zelle den Transistor K2 gesperrt und K1 bleibt leitend.

Soll das Flipflop den Binärwert 1 speichern, dann muss zum Schreiben die SL1-Leitung High Pegel und/oder die SL2-Leitung Low Pegel erhalten. In beiden Fällen wird der Transistor K2 leitend und hält K1 solange gesperrt, wie die Pegel der Schreib-Lese-Leitungen nicht geändert werden. Nach dem Deaktivieren der Zelle behält der Q-Ausgang den eingeschriebenen High Pegel.

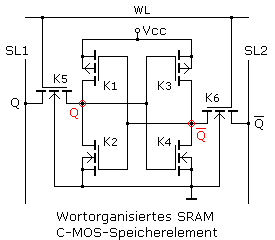

SRAM in C-MOS-Technik

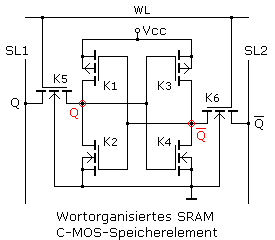

Die Schaltung zeigt ein Wort organisieres SRAM in C-MOS-Speichertechnik. Zwei sich gegenseitig steuernde C-MOS-Inverter bilden das Speicher-Flipflop. Mit zwei weiteren MOS-FET werden die Q und Q-Nicht Ausgänge der Speicherzellen wortorganisiert mit den Schreib-Lese-Leitungen im SRAM verbunden. Ein Zeilendecoder steuert die Wortleitung WL und aktiviert gleichzeitig alle Bitstellen des Datenworts.

Solange keine Schreib- oder Lesezugriffe erfolgen, bleibt der Strombedarf mit weniger als 100 nA sehr gering. Mithilfe einer Pufferbatterie kann ein Speicher-IC in C-MOS-Technik den Inhalt einige Jahre speichern. Mit einem Doppelschicht-(Goldcap)-Kondensator oder einer Lithiumbatterie bilden SRAM kleinerer Speicherkapazitäten ein kompaktes, nicht flüchtiges (non volatile) NVRAM-Modul. Mit externer Pufferbatterie speichern sie BIOS-Daten von PCs im sogenannten CMOS-RAM, besser BBSRAM (battery backed) Speicher.

Aktivieren zum Schreiben

Ein vom Zeilendecoder an die Wortleitung gelegter High Pegel aktiviert die angeschlossenen Zellen. Die Transistoren K5 und K6 schalten das Flipflop niederohmig an die Schreib-Lese-Leitungen. Soll die Zelle eine logische 0 speichern, so legt der Schreibverstärker an die SL1-Leitung Low Pegel und/oder High Pegel an die SL2-Leitung. Mit Q = 0 ist der Transistor K3 leitend und K4 gesperrt. Das Potenzial der Gate-Elektoden von K1 und K2 wird positiv, sodass K1 sperrt und K2 leitet. Der Ausgang Q des linken Inverters erhält Low Pegel und Q-Nicht des rechten Inverters High Pegel.

Der Speicherzustand bleibt auch nach dem Deaktivieren der Wortleitung und Sperren der Zugriffstransistoren K5 und K6 erhalten.

Soll die Zelle am Ausgang Q eine logische 1 speichern, dann muss der Schreibverstärker an SL1 High Pegel und/oder Low Pegel an SL2 legen. Bei aktivierter Wortleitung und SL2 (Q-Nicht) = 0 wird der Transistor K1 leitend und K2 gesperrt. Der Ausgang Q des linken Inverters erhält High Pegel und steuert damit die Gates von K3 und K4. Der Transistor K3 sperrt und K4 leitet, sodass der Ausgang Q-Nicht des rechten Inverters auf Low Pegel gehalten wird.

Aktivieren zum Lesen

Die Schreibverstärker werden beim Aktivieren der Wortleitung von den Schreib-Lese-Leitungen getrennt. Die Zugriffstransistoren K5 und K6 verbinden die Ausgänge Q und Q-Nicht der Flipflop Zelle niederohmig mit SL1 und SL2. Die nicht dargestellten Leseverstärker geben den Q und invertierten Q-Nicht Pegel durch ein UND Gatter an den Datenausgang. Mit Q = 1 ist das invertierte

Q-Nicht = 1, folglich hatte die Zelle eine logische 1 gespeichert.

△

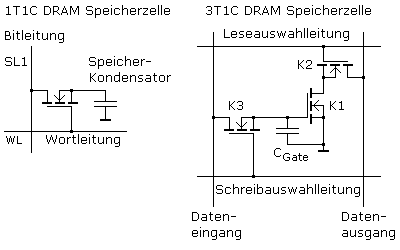

Dynamisches RAM

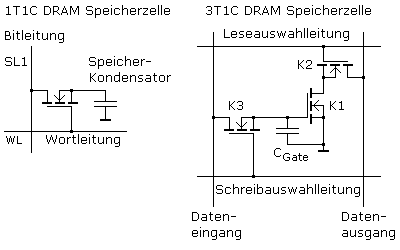

In einer dynamischen Speicherzelle, dynamic random access memory DRAM, wird die Information als Kondensatorladung gespeichert. Ein aufgeladener Kondensator entspricht der logischen 1, ein entladener Kondensator der logischen 0. Einer oder mehrere Transistoren schalten den Kondensator an die Schreib-Lese-Leitungen. Als Kondensator kann die Gatekapazität des

MOS-Transistors genutzt werden. Sie ist bei hoher Integrationsdichte zu klein, daher ist über oder neben der Sourceelektrode ein mit ihr verbundener Kondensator integriert. Da auch MOS-Transistoren im Sperrzustand keine idealen Nichtleiter sind, fließt Ladung ab. Der Ladezustand des Speicherkondensators muss regelmäßig aufgefrischt werden. Der Refresh-Zyklus erfolgt von einem eigenen Controller gesteuert alle 32 ms (maximal 64 ms). Während dieser Zeit ist die normale Speichernutzung unterbrochen.

- Burst-Refresh:

-

Der Refresh erfolgt für alle Speicherzellen gleichzeitig. Der normale Speicherbetrieb ist um 40 µs relativ lange unterbrochen.

- Cycle-Stealing:

-

Der Refresh erfolgt verteilt nacheinander auf jeweils nur eine Zeilenadresse. Durch ein WAIT-Signal gesteuert ist der normale Zugriff bei 128 Zeilen nur noch für rund 300 ns unterbrochen.

- Hidden-Refresh:

-

Der Refresh ist so auf den Prozessortakt synchronisiert und erfolgt nur, wenn dieser keine Speicherzugriffe ausführt. Die Speicherbausteine werden als (synchrone) SDRAM bezeichnet.

Die Speicherzellen sind vereinfacht gesehen in einer zweidimensionalen Matrix wortorganisiert angeordnet. Die Aktivierung der Zeile erfolgt mit dem row

address strobe RAS-Signal gefolgt von der Spaltenadresse, dem column address

strobe CAS-Signal zum Auslesen der gespeicherten Zustände. Zur Reduzierung der IC-Anschlüsse wird Multiplexing bei der Adressierung eingesetzt.

Vor dem Lesen der Speicherinhalte wird an alle Schreib-Lese-Leitungen, auch Bitleitungen genannt, ein Potenzial gelegt, das dem Mittelwert einer Zelle mit logisch 1 und logisch 0 entspricht.

Das verhindert den Einfluss unterschiedlicher Leitungskapazitäten, die oft ein Mehrfaches der Speicherkapazitäten betragen. Es findet ein Ladungsaustausch zwischen dem Leitungs- und Speicherpotenzial statt.

Der Spannungsunterschied zwischen High und Low beträgt am Eingang des Leseverstärkers um 100 mV und wird zu den normalen High und Low Ausgangspegeln gewandelt. Die Leseverstärker bilden eine

SRAM-Schaltung, um die Zellenzustände für den Refresh-Zyklus zu speichern. Links im Bild ist ein DRAM-Speicherelement mit einem Transistor und einem separaten integrierten Speicherkondensator dargestellt.

Die Schaltung im rechten Bildteil zeigt ein DRAM-Speicherelement mit drei n-Kanal MOS-FET. Hier wird die Gatekapazität als Speicherkondensator genutzt. Aufgrund des kleineren Kapazitätswerts muss der Refresh-Zyklus alle 2 ms erfolgen und die Integrationsdichte ist geringer als bei Speicher-ICs in der 1T1C-Technik.

Schreibprozess

Für den Lese- und Schreibvorgang gibt es getrennte Auswahl- und Datenleitungen. Soll in die Zelle eine logische 1 geschrieben werden, wird an den Dateneingang High Pegel gelegt. Mit High Pegel an der Schreibauswahlleitung wird der Transistor K3 leitend und lädt die Gatekapazität von K1 positiv auf. Danach sperrt ein Low Pegel an der Schreibauswahlleitung den Transistor K3 und die Zelle speichert den Binärwert High.

Leseprozess

An die Datenausgangsleitung wird High Pegel gelegt, der gleichzeitig den Einfluss der unterschiedlichen Leitungskapazitäten ausgleicht. Mit positiver Spannung an der Leseauswahlleitung wird der Transistor K2 leitend geschaltet. Das positive Potenzial der Datenleitung liegt jetzt am Drain des Speichertransistors K1. Ist sein Gate positiv geladen, und hat er eine logische 1 gespeichert,

dann leitet K1 und zieht das Potenzial der Datenausgangsleitung auf Masse. War das Gate bei einer gespeicherten logischen 0 nicht geladen, so bleibt K1 gesperrt und das Potenzial der Datenleitung behält den High Pegel. Der invertierte Datenausgangspegel entspricht der gespeicherten Information. Die Gateladung des Speichertransistors K1 wird den Leseprozess nicht geändert.

Refresh-Prozess

Mit einer eigenen Takt- und Steuerschaltung wird alle 2 ms der Ladezustand der Zelle gelesen. Wird eine logische 1 erkannt, dann schaltet sie den Transistor K3 niederohmig. Ein gleichzeitig an der Dateneingangsleitung anliegender High Pegel regeneriert den Ladezustand. Wird eine logische 0 gelesen, dann bleibt K3 gesperrt und der Low Pegel der Zelle erhalten.

Auch mit dieser umfangreichen Zusatzsteuerung arbeiten DRAM Speicher sehr zuverlässig. Vorteilhaft ist die hohe Integrations- und Speicherdichte der 1T1C-Zellen. Nachteilig sind die längeren Schaltzeiten, die es zwischen der Adressierung und dem Datenerhalt gibt, da während des Refresh-Zyklus die normalen Schreib-Lesezugriffe gesperrt bleiben. Wichtig ist das Einhalten des vom Hersteller angegebenen Temperaturbereichs. Mit steigender Arbeitstemperatur nimmt der Leckstrom und damit die Entladung der Speicherkapazität zu. Im Konsumerbereich liegt der obere Temperaturbereich bei

70 ... 85 °C.

△

Festwertspeicher

Festwertspeicher mit wahlfreiem Zugriff sind vom Hersteller vorprogrammiert oder vom Nutzer einmalig programmierbar. Die gespeicherten logischen Zustände lassen sich beliebig oft lesen.

Die Speicher-ICs werden als read only memory ROM bezeichnet. Fast immer sind es wortorganisierte Speicherbausteine,

die zwischen der Wort- und Bitleitung eine oder keine Verbindung herstellen. Die Koppelelemente können Dioden, bipolare Transistoren oder MOS-FET sein.

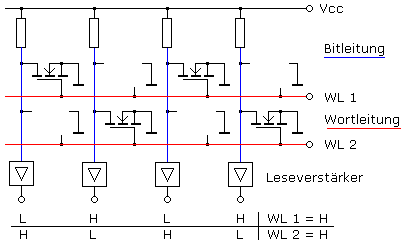

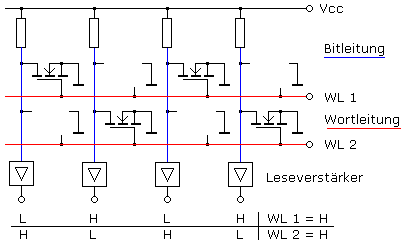

Maskenprogrammierung

Speicher-ICs in großer Stückzahl zum Beispiel für Fernbedienungen, Schreibtastaturen oder sehr schnelle Analog-Digital-Wandler zur Digitalisierung analoger Videosignale erhalten ihre Informationen durch Maskenprogrammierung. Die immer konstanten Datenworte sind dauerhaft gespeichert und stehen unmittelbar beim Aktivieren der Wortauswahlleitung an den Datenausgängen bereit. Eine aufgelegte Maske bestimmt beim Ätzprozess, wo aktive Koppelelemente zwischen den Wort- und Bitleitungen entstehen und wo sie fehlen. Maskenprogrammierte ROM in MOS-Technik erlauben eine sehr hohe Integrations- und Speicherdichte und zeichnen sich durch einen sehr geringen Leistungsbedarf aus.

Die Skizze zeigt den Ausschnitt eines maskenprogrammierten ROM in MOS-Technik. Mit einem High Pegel wird immer nur eine Wortleitung aktiviert. Sind Transistoren als Koppelelemente vorhanden,

dann schalten sie die Bitleitung nach Masse und der Eingang des Leseverstärkers erkennt Low Pegel. Wo im Datenwort der Transistor fehlt, bleibt auf der Bitleitung der High Pegel bestehen.

Die Leseverstärker sind kein notwendiger Bestandteil des PROM.

△

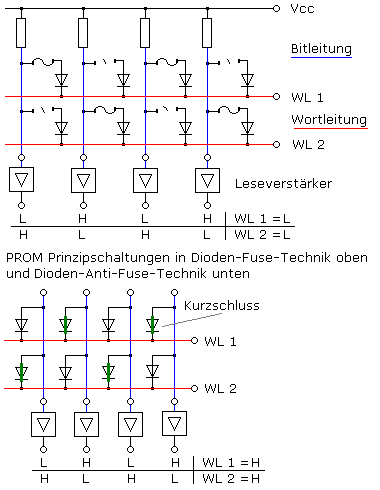

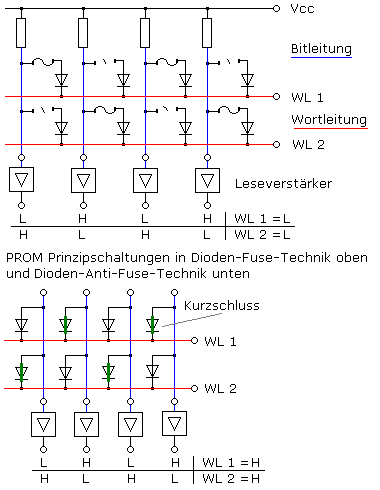

PROM – Programmierbare Festwertspeicher

Da die Maskenprogrammierung für kleinere Stückzahlen und spezielle Anwendungen nicht rentabel ist, wurden Speicher-ICs entwickelt, die vom Nutzer einmalig programmierbar sind und danach als ROM

arbeiten. Sie werden als programmable read only memory PROM bezeichnet. Die Zellen sind als

Dioden- oder Transistormatrix aufgebaut, deren Verbindungspunkte bei der Programmierung nicht umkehrbar hochohmig oder niederohmig zerstört werden.

Die Programmierung erfolgt in einem externen Programmiergerät mit einer ausreichend hohen Programmierspannung, die deutlich oberhalb der normalen Betriebsspannung liegt. In einer Variante ist jedes Zellenelement mit einem sehr dünnen Chrom-Nickel-Sicherungsdraht verbunden, der bei der Programmierung überlastet und hochohmig zerstört wird. Die dabei freigesetzten Metallatome könnten aber im späteren Betrieb durch die anliegenden unterschiedlichen elektrischen Potenziale wandern und die Leitfähigkeit der Kristallgitter negativ beeinflussen. Einzelne Bits der gespeicherten Informationen würden dann verloren gehen.

Bei definierter Überlastung bildet ein pn-Übergang in Siliziumtechnik einen Kurzschluss. Die Speicher-ICs wurden in entsprechender Diodenmatrix hergestellt, um die Langzeitstabilität des eingespeicherten Programms zu verbessern. Zur Programmierung wird die Wortleitung auf Massepotenzial gelegt und ein Spannungsimpuls auf der jeweiligen Bitleitung führt zum Kurzschluss der Diode.

Das Lesen der Informationen erfolgt mit High Pegel an der Wortleitung. Die intakten Diodenstrecken leiten nicht und am Datenausgang wird Low Pegel erkannt. Derzeit vermeidet man diese Materialveränderungen und stellt PROMs als einmalig programmierbare EPROMs ohne Quarzfenster her.

△

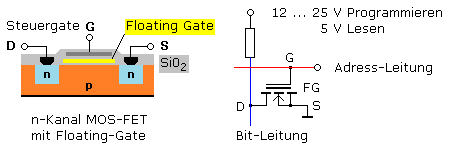

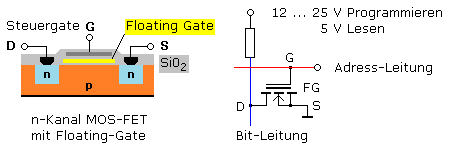

EPROM Festwertspeicher

Die Speichertransistoren, meistens in n-Kanal MOS-FET Technik gefertigt, haben ein zusätzliches vollkommen isoliertes Gate. Es wird als Floating-Gate bezeichnet und bestimmt mit seiner elektrischen Ladung den Speicherzustand der Zelle. Nach der Herstellung und im gelöschten Zustand ist das Floating-Gate ladungsneutral. Die Bezeichnung FAMOS-Speicher floating gate

avalanche injection MOS gibt einen Hinweis auf den Prozess der Ladungsübertragung. Der Speicherbaustein hat über dem Chip ein Quarzglasfenster. Das EPROM erasable programmable ROM ist mit energiereicher UV-C Strahlung (254 nm einer Hg-Spektrallinie) komplett löschbar und kann danach neu programmiert werden. Das im voranstehenden Absatz erwähnte einmalig programmierbare PROM (OTP, one time programmable) ist ein nicht löschbares EPROM. Das Löschen und Programmieren erfolgt in einem externen Programmiergerät.

Programmierung nach dem HCI-Verfahren

Programmiert wird mit einer hohen Spannung, die sowohl am Drain und am Steuergate anliegt. Der Transistor leitet mit hohem Drain-Source-Kanalstrom, der die Elektronen stark beschleunigt.

Diese schnellen Elektronen (hot electrons) können sowohl die Energiebarriere zum Leitungsband der Siliziumdioxid-Isolierschicht überwinden als auch durch Stoßionisation weitere Ladungsträgerpaare erzeugen. Energiereiche Elektronen aus diesem Lawineneffekt (Avalanche-Effekt) gelangen ebenfalls in das Leitungsband. Das Dielektrikum zwischen dem Floating-Gate und dem Kanal ist mit rund 50 nm sehr dünn und die von der hohen Spannung am Steuergate bedingte Feldstärke entsprechend groß. Sie zieht die Elektronen aus dem Leitungsband auf das Floating-Gate und lädt es negativ auf. Das Verfahren wird hot-carrier injektion HCI und Avalanche-Effekt genannt. Die Ladung bleibt nach dem Abschalten der Programmierspannung erhalten.

Leseverfahren

Zum Lesen der gespeicherten Information liegt die niedrige, meistens 5 V Spannung an der Adressleitung an, die den Transistor mit dem negativ geladenen Floating-Gate nicht mehr leitend schalten kann. Das Potenzial auf der Bitleitung wird nicht nach Masse gezogen und bleibt auf High Pegel.Eine Zelle mit nicht geladenem Floating-Gate leitet und die Bitleitung wechselt auf Low Pegel.

Löschverfahren

Mit kurzwelliger, energiereicher Strahlung kann sich das Floating-Gate entladen. Zum Löschen des gesamten EPROM-ICs wird es zwischen 10 bis 30 Minuten durch das Quarzfenster mit kurzwelligem UV-Licht von rund 0,1 Ws/mm2 bestrahlt. Die energiereichen Photonen erzeugen in der Isolierschicht Elektronen-Lochpaare und die im Floating-Gate gespeicherte Ladung kann bei anliegender Spannung abfließen. Die Photonenleistung erzeugt immer einige bleibende Fehlstellen im Kristallgitter der Siliziumdioxid Isolierung, daher sind die Löschzyklen auf einige 100 Mal begrenzt. Da auch im Spektrum normaler Beleuchtung kurzwellige Anteile in geringer Intensität vorkommen, sollte nach dem Löschen das Quarzfenster lichtdicht verschlossen werden. Die Hersteller versprechen einen Datenerhalt von 10 Jahren.

△

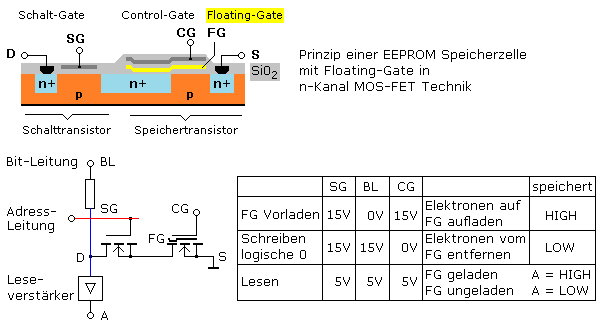

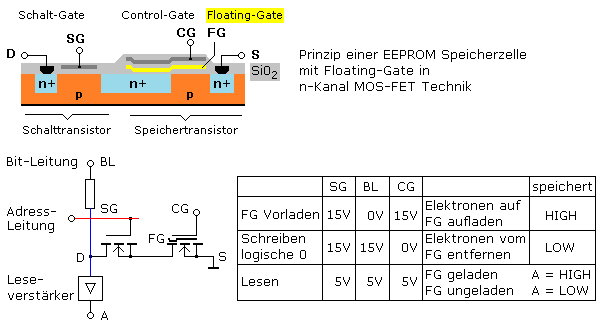

EEPROM Festwertspeicher

Das Programmieren und Löschen erfolgt ohne externes Programmiergerät in der Einsatzschaltung. Die höhere Programmierspannung wird auf dem Chip selbst erzeugt. Die Bezeichnung EEPROM

electrically erasable PROM weist auf den komplett elektrisch gesteuerten Programmierprozess hin. Jeder Speichertransistor hat einen vorgeschalteten Schalttransistor. Das Floating-Gate (FG) des Speichertransistors liegt mit sehr geringem Isolationsabstand teilweise über dem stark n-dotierten Drainbereich.

Die Ladungsverschiebung auf das Floating-Gate erfolgt nach einem von Fowler und Nordheim mathematisch beschriebenen quantenmechanischen Tunneleffekt. Es handelt sich um eine Feldemission,

die bei großer elektrischer Feldstärke (>109 V/m) Elektronen aus einem negativen Bereich in Richtung des positiven Feldbereichs zieht. Die Oxidschichtdicke ist nur im Bereich des Tunneleffekts mit (10 ... 30) nm sehr gering und sonst um drei bis vier Mal dicker. Diese Speichertransistoren werden als FLOTOX-Speicher bezeichnet

(floating gate tunnel oxide). Der Skizze nach kommt das 'Drain Side Tunneling' zur Anwendung, da das FG mit dem geringsten Abstand über dem negativ dotierten Drainbereich liegt und von dort geladen wird. Beim 'Uniform Tunneling' erfolgt die Feldemission zwischen dem Substrat und Gate. Für das Gate wird Polysilizium anstelle von Metall verwendet.

Der Grundzustand der Speicherzelle ist ein geladenes Floating-Gate. Beim Tunneleffekt fließt kein Kanalstrom da Drain D und Source S beide auf Massepotenzial liegen. Die Adressleitung mit dem Gate des Schalttransistors und das Steuergate CG des Speichertransistors erhalten die Programmierspannung. Der Schalttransistor leitet und der Drainbereich des Speichertransistors liegt ebenso wie sein Sourceanschluss auf Masse. Die Programmierspannung an CG verursacht den Tunneleffekt und zieht Elektronen aus dem Drainbereich auf das FG. Es speichert negative Ladung und erhöht damit das Potenzial zwischen Gate und Source, um diesen Transistor leitend zu schalten.

Das Floating-Gate kann entladen und somit umprogrammiert werden, wenn an der Adress- und Bitleitung die Programmierspannung anliegt und das Control-Gate Massepotenzial hat. Der Schalttransistor leitet und die Drainspannung unter dem FG ist gleich der Programmierspannung. Der Speichertransistor bleibt mit CG = 0 V gesperrt. Die vom Drain ausgehende hohe Feldstärke zieht mit dem Tunneleffekt die negative Ladung vom FG ab.

Mit dem Anlegen der normalen niedrigen 5 V Betriebsspannung an die Wort- und Bitleitung wird der Schalttransistor leitend. Mit ebenfalls 5 V am Control-Gate wird der Speicherzustand gelesen. Ist das Floating-Gate negativ geladen, so bleibt der Transistor gesperrt und die Spannung auf der Bitleitung hoch. Der Leseverstärker gibt High Pegel aus. Ist keine Ladung auf dem FG gespeichert,

dann wird der Transistor leitend geschaltet und zieht die Spannung der Bitleitung nach Masse. Der Leseverstärker gibt Low Pegel aus.

Zur beschriebenen Arbeitsweise, die nur das Fowler-Nordheim-Tunnelverfahren nutzt, gibt es weitere Verfahren, die sowohl den Tunneleffekt als auch das HCI-Avalanche-Verfahren anwenden.

Das Programmieren ist mit einigen Millisekunden relativ langsam. Viele Hersteller geben einen Datenerhalt von mehr als 10 Jahren an. Beide Verfahren erzeugen bleibende Fehlstellen im Dielektrikum und mindern sein Isolationsvermögen.

Die garantierte Zahl der Programmierzyklen wird auf einige 1000 bis 10000 angegeben. Je dünner die Oxidisolierung ist, desto eher machen sich die Fehler bemerkbar.

△

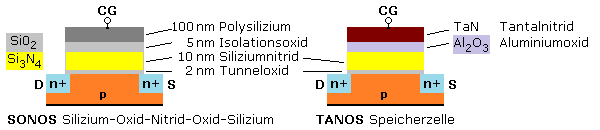

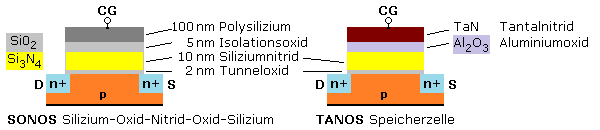

MNOS-FET Festwertspeicher

Die Arbeitsweise dieser Speicherzelle ist vergleichbar mit dem Floating-Gate Transistor. Die Ladungsanreicherung erfolgt nicht mehr auf einem leitfähigen Polysilizium- oder metallischen Gate,

#sondern in einem keramischen Nichtleiter aus Siliziumnitrid. MNOS steht für metal nitride oxide

semiconductor wo jetzt anstelle des Metalls Silizium (SNOS) als Halbleiter verwendet wird. Das Siliziumnitrid Si3N4 wird in der Chiptechnologie oft als Trenn- und Isolierschicht eingesetzt und kann positive und negative Ladungsträger reversibel abfangen. Das Siliziumnitrid wirkt als Ladungsfalle und die Speicherzelle wird daher auch als Charge-Trapping-Speicher (CT-Memory, CTF) bezeichnet.

Die Tunneloxidschicht kann auf wenige Nanometer verringert werden, wodurch sich die Speicherzeit verkürzt. Die durch Speicherzyklen hervorgerufenen bleibenden Isolationsschäden im Tunneloxid haben fast keinen Einfluss mehr, da die darüberliegende Siliziumnitrid Speicherschicht ein sehr guter Isolator ist. Die eingelagerten Ladungsträger sind nicht wie Floating-Gate aus Polysilizium frei beweglich. Es kann sich nur die unmittelbar an der Schadstelle gespeicherte Ladung ausgleichen, während benachbarte Speicherladungen den Speicherzustand aufrechterhalten.

Die Programmierung nutzt mit dem HCI-Verfahren einen direkten Tunneleffekt oder mit geringerer Programmierspannung das zeitlich länger dauernde Fowler-Nordheim-Tunnelverfahren. Gelangen bei einem

n-Kanal Transistor und positiver Programmierspannung am Steuergate CG Elektronen in die Ladungsfalle, bleibt der Transistor nach der Programmierung gesperrt. Der Zellinhalt kann gelöscht werden,

wenn mit einem negativen Spannungspuls am CG Defektelektronen (Löcher) in die Speicherschicht gelangen und mit den Elektronen rekombinieren. Der gespeicherte Ladezustand bleibt mehr als 10 Jahre erhalten. Die Zahl der Ladezyklen soll einige Zehntausend betragen.

Der Einsatz anderer Materialien soll die SONOS-Zelle optimieren. Das Polysiliziumgate wird durch Tantalnitrid TaN, eine elektrisch leitende Metallkeramik, ersetzt. Sie hat eine höhere Austrittsarbeit für Elektronen. Aluminiumoxid als Gate-Isolator ersetzt das Siliziumdioxid. Mit der im Vergleich zum SiO2 geringeren elektrischen Feldstärke im

Al2O3 verringert sich die Zahl der bleibenden Isolationsdefekte. Durch die größere Austrittsarbeit und die kleinere Feldstärke können beim Löschen keine Elektronen mehr vom Gate in die Nitridspeicherschicht gelangen. Die zu überwindenden Energieniveaus liegen näher beieinander und zum Programmieren der Zelle muss weniger Energie aufgewendet werden.