MOS-Feldeffekttransistor

Die Gate-Elektrode ist im Feldeffekttransistor, FET elektrisch leitend mit dem Halbleitermaterial verbunden. Im MOS-FET ist die Gate-Metallelektrode durch eine dünne Oxidschicht vom Halbleiter getrennt. Das Oxid ist Quarz, Siliziumdioxid und ein extrem guter Isolator. Die Bauteilbezeichnung steht für Metall-Oxide-Semiconductor-Feldeffekt-Transistor.

Vom Halbleitermaterial her unterscheidet man zwischen dem p-Kanal MOS-FET und n-Kanal MOS-FET. Von der Bauart abhängig gibt es Anreicherungs- und Verarmungstransistoren. Der Anreicherungstyp, englisch enhancement, oder selbstsperrender MOS-FET ist ohne Ansteuerung nicht leitend und aus technologischen Gründen meistens ein p-Kanal-Transistor. Der Verarmungstyp, englisch depletion, ist wie ein "normaler" FET selbstleitend und fast immer ein n-Kanal-Typ. Beide Arten werden für eine Schwellenspannung zwischen 0,8 ... 2 V, charakterisiert als Niedervolttechnik und 2,5 ... 4 V als Hochvolttechnik hergestellt. Innerhalb dieses Spannungsbereichs zwischen Gate und Source wird der Kanal gerade abgeschnürt oder gerade geöffnet. Die MOS-FET-Technologie hat eine besondere Bedeutung in der monolithischen Großintegration bei der Chipherstellung erlangt. Sie gestattet eine hohe Integrationsdichte bei sehr geringer Fehlerrate und einem kleinen Leistungsverbrauch, da die Ansteuerung stromlos erfolgt.

Selbstleitender MOS-FET

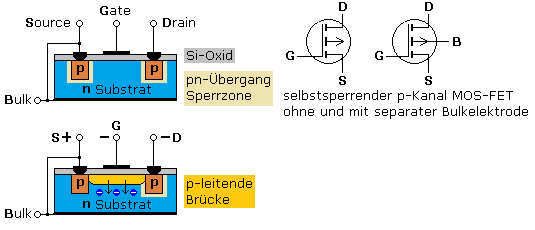

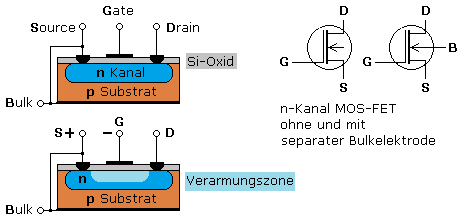

Auf einem p-Trägermaterial, dem Substrat, englisch als Bulk bezeichnet, befindet sich eine schwach n-leitend dotierte Zone. Sie ist mit den Elektroden Drain und Source elektrisch leitend verbunden. Dazwischen liegt durch die Oxidschicht isoliert die Gateelektrode. Manchmal ist das Substrat intern mit Source leitend verbunden, oft ist dafür eine vierte Elektrode herausgeführt. Dieser MOS-FET verhält sich in vielen Eigenschaften wie ein FET, allerdings mit isoliertem Gate und wird daher auch als IG-FET bezeichnet.

Im Schaltzeichen steht die Gateelektrode vergleichbar mit einer Kondensatorplatte dem Kanal gegenüber. Der Kanal veranschaulicht mit seiner durchgezogenen Linie die Selbstleitfähigkeit. Bei Ansteuerung entsteht zwischen der Gateelektrode und dem Kanal ein elektrisches Feld, das Elektronen aus dem n-Kanal in das p-Substrat verdrängt. Es bildet sich eine Verarmungszone, die den selbstleitenden n-Kanal bis zur Abschnürung verengt und hochohmiger werden lässt.

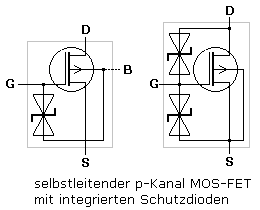

Im FET bildet sich durch die Sperrzone des pn-Übergangs zwischen Gate und Source eine elektrische Isolierung. Ein Umpolen der Gatespannung würde die Sperrzone abbauen und den FET zerstören. Der MOS-FET besitzt eine permanente Isolierschicht, die auch durch Potenzialumkehr am Gate bestehen bleibt. Wird für den oben dargestellten MOS-FET das Gate positiv, so zieht das elektrische Feld Ladungsträger aus dem p-Substrat in den n-Kanal hinein. Seine Leitfähigkeit nimmt dann wegen der Anreicherung mit Ladungsträgern zu.

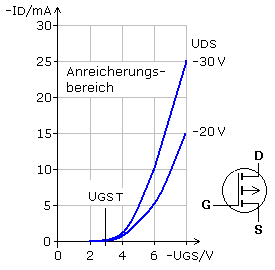

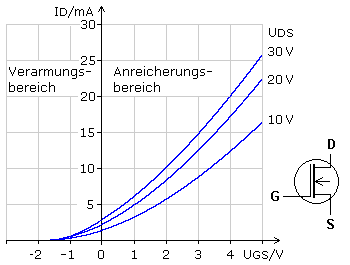

Das Diagramm zeigt ein typisches Eingangskennlinienfeld für einen n-Kanal IG-FET in Niedervolttechnik. Die Schwellenspannung beträgt hier −UGS P = 1,6 V. Die Kennlinien des selbstleitenden n-Kanal MOS-FETs verlaufen für negative Gate-Source-Spannungen im Verarmungsbereich und für positive Steuerspannungen im Anreicherungsbereich. Ist der Substratanschluss aus dem Gehäuse herausgeführt, kann mithilfe einer zusätzlichen Bulk-Source-Spannung das Kennlinienfeld beeinflusst werden. Das Ausgangskennlinienfeld entspricht dem eines selbstleitenden FET, wobei der Parameter UGS mit beiden Polaritäten vorhanden ist.

△