Taktzustandsgesteuerte RS-Flipflops

Der Ausgangszustand eines asynchronen Flipflops reagiert auf Änderungen seiner Eingangszustände. Mit einem zusätzlichen Steuer- oder Triggersignal kann die Information des Binärspeichers gezielt gesetzt oder abgerufen werden. Erfolgt die Steuerung mit einem statischen High oder Low Taktzustand, werden diese Speicher in die Gruppe der taktzustandsgesteuerten RS-Flipflops eingeordnet. Da der Taktpegel über einen längeren Zeitraum >100 ns bestehen bleibt, ist auch die Bezeichnung Taktpegelsteuerung gebräuchlich.

Im englischen Sprachbereich werden taktzustandsgesteuerte Speicherbausteine als Latch und taktflankengesteuerte Speicher als Flipflop bezeichnet. Die unterschiedliche Taktsteuerung beeinflusst auch das Schaltverhalten der Speicher. In diesem Webprojekt bleibt die Bezeichnung beim taktzustandsgesteuerten Flipflop. Die Voraussetzungen zur Taktflankensteuerung sind im Webprojekt an anderer Stelle beschrieben.

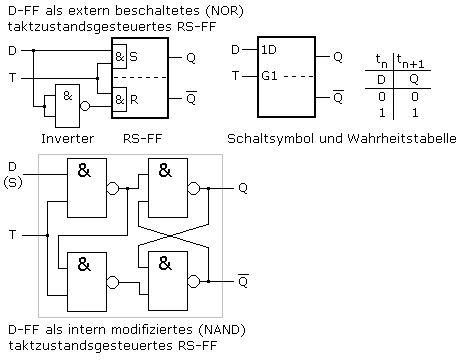

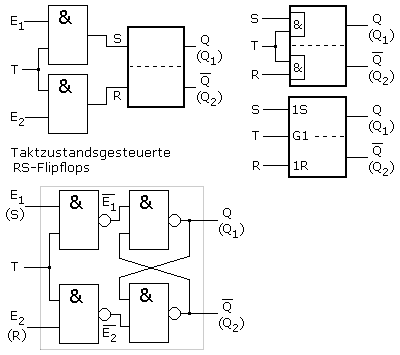

Ein aus vier NAND-Gattern aufgebautes RS-FF ist High-aktiv. Trennt man die gemeinsamen NAND-Eingänge auf und schaltet sie wie oben im Bild zu einem neuen Eingang, dem Takteingang zusammen, entsteht ein taktzustandsgesteuertes RS-FF. Zum gleichen Ergebnis kommt man, wenn man vor jeden Eingang eines aus NOR-Gattern aufgebauten RS-FF ein UND-Gatter schaltet und je einen Eingang, wie unten im Bild, zum Takteingang zusammenfasst.

Die Schaltzeichen der taktzustandsgesteuerten RS-Flipflops sind rechts dargestellt. G steht für die UND-Verknüpfung. Die nachstehende Ziffer bei G1 kennzeichnet ihn als steuernden Eingang. Die Ziffern vor den Eingängen 1S und 1R zeigen, dass beide vom gleich bezifferten Eingang gesteuert werden.

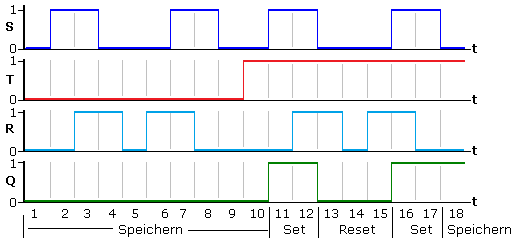

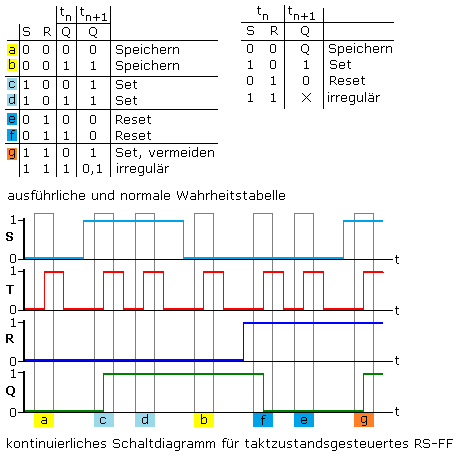

Das folgende Bild zeigt ein Schaltdiagramm für aufeinanderfolgende einstellbare Eingangskombinationen. Die Zustandsänderungen sind das Ergebnis einer Schaltungssimulation. Untersucht wurde ein aus NAND-Gattern aufgebautes RS-FF (siehe oben). Begonnen wurde mit allen Eingängen auf Low Pegel.

In den Fällen 1 ... 9 bleibt mit dem Taktsignal T = 0 der Ausgangszustand Q unverändert. Die UND-Verknüpfung am Eingang verhindert Pegeländerungen am internen NAND-Latch. Aus gleichem Grund bleibt auch für den Fall 10 mit S = 0 und R = 0 und dem Taktwechsel auf T = 1 das Vorsignal gespeichert.

Im Fall 11 wird bei anliegendem Takt T = 1 der Speicher mit dem Wechsel auf S = 1 gesetzt. Das gleiche Ergebnis stellt sich ein, wenn zuerst S = 1 anliegt und dann der Takt auf High schaltet. Die Fälle 12 und 16, wo alle Eingänge auf High liegen, sollte vermieden werden. Sie ergeben einen Set-Zustand und schränken nur dann die weitere korrekte Arbeitsweise des RS-FF nicht ein, solange im Folgeschritt das Taktsignal nicht nach Low wechselt. Bei einem Taktwechsel versagt das Simulationsprogramm. In einer Hardwareschaltung bestimmt ein schneller arbeitendes Eingangsgatter den folgenden Ausgangszustand. Da dieser nicht sicher reproduzierbar ist, sind S = 1 und R = 1 vor einem Taktwechsel unbedingt zu vermeiden.

Ein Reset erfolgt mit S = 0 und R = 1 beim Taktwechsel auf High oder wie im Fall 15 bei T = 1 und dem Wechsel des Reset-Eingangs auf High. Bei der Taktsteuerung erscheint es sinnvoll aus dem Speicherzustand mit T = 0 neue Eingangszustände zu schalten, die mit dem Taktwechsel auf T = 1 zum Folgezustand am Ausgang Q führen. Die Schaltdiagramme lassen sich dann als übersichtlichere Wahrheitstabelle schreiben.

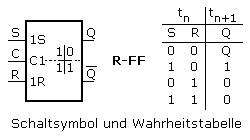

Wahrheitstabellen

Nach der Definition sollen beim Flipflop die beiden Ausgangszustände zueinander entgegengesetzt sein. In der Wahrheitstabelle wird daher nur der Ausgangszustand für Q (Q1) geschrieben. Er wird zur Zeit tn vor dem Eintreffen des Taktsignals und zur Zeit tn+1 nach dem auslösenden Taktsignal notiert. Meistens ist die verkürzte Schreibweise der Wahrheitstabelle ausreichend.

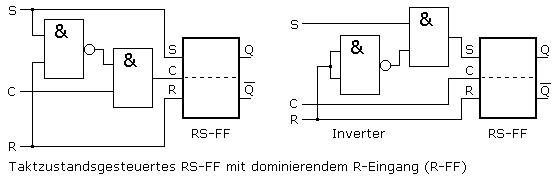

RS-Flipflop mit dominantem R-Eingang

Nur das asymmetrische Ansteuern der RS-FF Eingänge ergibt beim Wechsel des Taktpegels einen vorhersagbaren Ausgangszustand. Mit Zusatzschaltungen kann die Fehlfunktion bei der irregulären Eingangskombination S = R = 1 verhindert werden. Nach dem Taktwechsel speichert das R-Flipflop bei gleichen Eingangspegeln den vorherigen Zustand. Der Zustand am R-Eingang dominiert das Verhalten des RS-FF. Das Bild zeigt zwei Eingangsschaltungen, die aus einem RS-FF ein taktzustandsgesteuertes R-FF machen.

In der Schaltung links gelangt das Taktsignal durch ein UND-Gatter an das RS-FF. Das vorgeschaltete NAND-Gatter sperrt bei S = R = 1 das UND-Gatter und verhindert die Weiterleitung des Taktsignals an das RS-FF. Mit C = 0 speichert das RS-FF den vorangegangenen Zustand. Mit asynchroner Eingangssteuerung wird jeder Taktwechsel am RS-FF wirksam.

In der rechten Schaltung wird das RS-FF vom Taktsignal direkt gesteuert. Ein als Inverter geschaltetes NAND-Gatter sorgt dafür, dass am RS-FF die Eingangszustände zueinander immer invertiert sind. Mit S = R = 1 sperrt der Inverter die Weiterleitung von S = 1 durch das UND-Gatter. Beim Taktwechsel erfolgt ein Reset. Mit S = 1 und R = 0 ist das UND-Gatter offen und mit C = 1 wird das RS-FF gesetzt. Das besondere Schaltverhalten bei S = R = 1 ist im Schaltsymbol eingetragen. Mit dem steuernden Takt C = 1 stellt sich am Flipflop Ausgang der Reset-Zustand mit Q1 = 0 und Q2 = 1 ein.

D-Flipflop

Wird beim RS-FF das S-Signal invertiert an den R-Eingang gelegt, so erhält man ein D-Flipflop. Sie gibt es als fertige ICs, wo beim RS-FF die Zusatzschaltung intern vorhanden ist, wie zum Beispiel beim TTL-Typ 7475 mit vier taktgesteuerten D-FFs. Ein D-FF hat nur noch einen vom Takteingang gesteuerten Signaleingang. Das als Daten anliegende Eingangssignal erscheint erst mit dem Taktwechsel auf High am Ausgang. Die Bezeichnung D-Flipflop geht entweder auf das Datensignal oder der vom Takt abhängigen, verzögerten (delay) Weiterleitung zurück. Solange der Taktzustand C = 1 ist, bleibt das Tor offen und Datenwechsel oder deren Pegelstörungen gelangen an den Ausgang. Das Taktsignal ist dem Eingangssignal übergeordnet. Das D-FF speichert seinen Ausgangszustand, solange der Taktzustand C = 0 bleibt. Es kann keine irregulären Eingangszustände geben.