Frequenzteiler

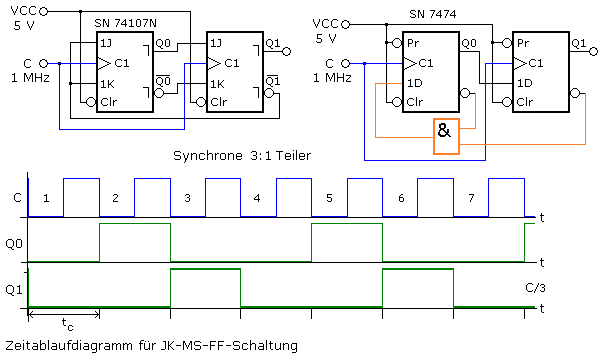

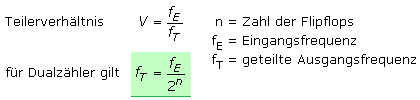

Auf den Zähltakt am Eingang bezogen erzeugt das Ausgangssignal eines Speicher-FF die halbe Frequenz. Die einzelnen Ausgänge der Dualzähler stehen mit dem Eingangstakt in einem festen Teilerverhältnis. Zähler sind folglich auch Frequenzteiler und können asynchron oder synchron vom Takt gesteuert werden. In besonderen Fällen werden beide Taktsteuerungen auch gemischt angewendet. Bei Dualzählern entspricht das Teilerverhältnis der 2er-Potenzreihe und errechnet sich aus dem Quotienten der Taktfrequenz zur Ausgangsfrequenz.

Die maximale Eingangsfrequenz asynchron gesteuerter Teiler wird von den Signallaufzeiten tp (propagation delay) und der Anzahl der Gatter bestimmt. Für ein fehlerfreies Arbeiten gilt: fE ≥ (n + 1) · tp . Synchrone Teiler können mit höheren Eingangsfrequenzen arbeiten.

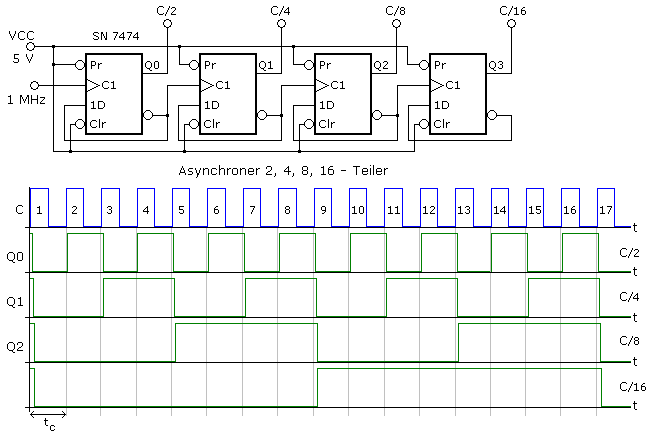

Asynchrone Frequenzteiler

Der asynchrone Dualzähler ist gleichzeitig ein Frequenzteiler mit festen, geradzahligen 2, 4, 8, 16, ... Teilerverhältnissen. Die Ausgangssignale aller Teilfrequenzen sind symmetrische 1:1 Rechtecksignale, solange die Eingangsfrequenz deutlich unterhalb ihres Maximalwerts liegt. Der dargestellte Frequenzteiler arbeitete in der Simulation bis maximal 24 MHz fehlerfrei. Ab 5 MHz lag der Tastgrad der ersten Teilerstufen deutlich erkennbar nicht mehr bei 50%, erfüllte aber die Teilerverhältnisse.

Rückwärtszähler funktionieren ebenso, nur sind die Teilersignale zueinander phasenverschoben. Mit Zusatzschaltungen lassen sich auch andere gerade und ungerade Teilerverhältnisse einstellen. Am höchst wertigen Ausgang eines BCD-Zählers ist die Eingangsfrequenz auf 1:10 mit einem Tastgrad von 20% geteilt.

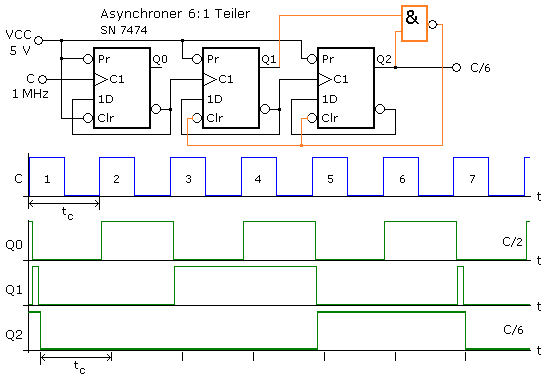

Asynchrone 6:1-Teiler

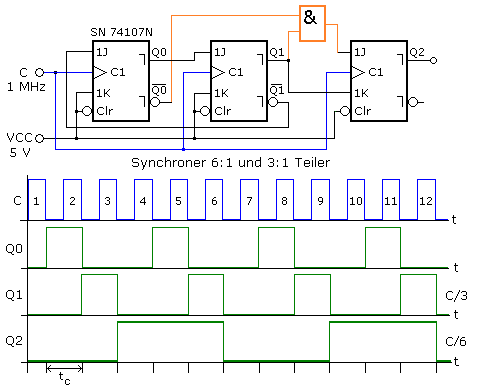

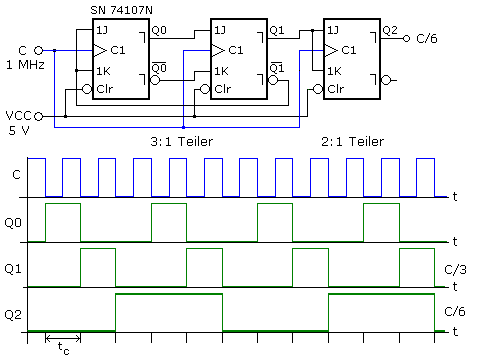

Drei Speicher-FF und eine Reset-Schaltung ergeben einen 6:1-Teiler und mit einem Tastgrad von 33% ein unsymmetrisches Puls-Pause-Signal. Mit dem 7. Takt wird Q1 = 1 und mit dem noch bestehenden Ausgangspegel Q2 = 1 gibt das NAND Gatter den Reset-Impuls, der die Ausgänge der beiden letzten Speicher-FF auf Low setzt.

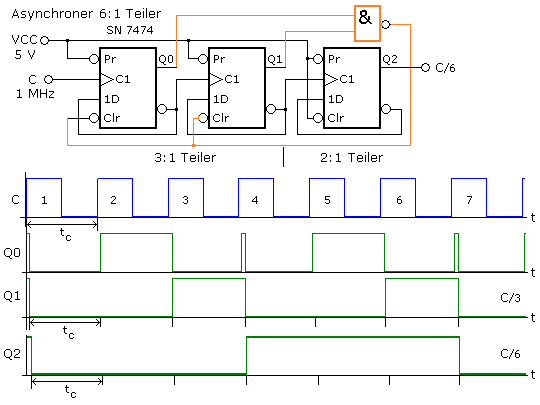

Ist für nachfolgende Anwendungen nur die geteilte Ausgangsfrequenz wichtig, muss die Phasenverschiebung zum Eingangstakt als Folge der Signallaufzeiten (propagation delay) nicht beachtet werden. Die Schaltung kann in einen 3:1-Teiler geändert werden, der den Takt für das dritte Speicher-FF stellt und nochmals halbiert. Der Eingangstakt ist dann 6:1 mit gleichem Puls-Pause-Verhältnis geteilt.

Taktgeber sind die Q-nicht Ausgänge der Flipflops. Die Zeitablaufdiagramme zeigen den Signalverlauf der Q-Ausgänge zu denen die Q-nicht Pegel gespiegelt sind. Das Ausgangs-FF kippt nach der steigenden Q1-nicht Flanke. Mit dem vierten Takt erfolgt der Reset vom NAND Gatter für den 3:1-Teiler, wodurch Q1-nicht auf High Pegel wechselt und der Ausgangspegel Q2 kippt.

Taktgeber in Digitaluhren

Mit mehreren Dualzählern und Decoderschaltungen für 7-Segmentanzeigen lassen sich Digitaluhren aufbauen. Notwendig ist ein genauer Sekundentakt zum Ansteuern eines Modulo-60-Zählers. Er stellt das Clocksignal für die Minuten- und Stundenzähler. Schaltungsbeispiele sind im Kapitel der Asynchronen Modulo-n-Zähler beschrieben. Für eine vertretbar genaue Zeitanzeige bedarf es eines stabilen Taktsignals somit sind Schaltungen mit dem 555-Timer-IC sind auf Dauer weniger gut geeignet.

Recht gut eignet sich die 50 Hz Frequenz des europäischen Stromverbundnetzes. Sie wird sowohl im Kurz- als auch im Langzeitbereich sehr genau auf den Sollwert 50,0 Hz geregelt. Die zum Sollwert sehr symmetrisch verlaufenden mittleren Abweichungen liegen um ±50 mHz, seltener bei ±100 mHz. Weitere Informationen finden man bei www.netzfrequenzmessungen.de. Mit zwei SN 7490A, die je einen 2:1 und 5:1 Teiler enthalten, kann der Sekundentakt generiert werden. Dieses Prinzip kam vielfach in netzabhängigen Digitaluhren zum Einsatz. Ohne statistischen Ausgleich würde die Fehlanzeige bei 1,5 Minuten pro Tag liegen.

Mit einer Batterie betriebene mobile Digitaluhren oder mit Analoganzeige und digitalem Schrittmotorantrieb generieren ihren Sekundentakt aus einer Quarzfrequenz. Die Resonanzfrequenz der meisten Uhrenquarze beträgt 32,768 kHz mit einer Genauigkeit von ±20 ppm, wobei 1 ppm = 0,0001% bedeutet. Ohne statistischen Ausgleich liegt der Anzeigefehler pro Tag etwas unter 2 Sekunden. Diese Quarzfrequenz entspricht 2^15 und kann daher sehr gut mit dem CMOS-IC CD 4060, einem 14-stufigen Asynchronteiler, auf 2 Hz geteilt werden. Ein in Reihe geschaltetes Flipflop liefert dann den Sekundentakt.

Selten wurden in hochwertigen Uhren 4,19 MHz Quarze verwendet. Hier kann mit dem CMOS-IC CD 4521, einem 18- bis 24-stufigen Teiler direkt auf den 1 Hz Sekundentakt geteilt werden (2^22 = 4,19 MHz).